Hybrid Linearized Class-BD Double Sided (LBDD) Digital Pulse Width Modulator (DPWM) for Class-BD Audio Amplifiers

DOI:

https://doi.org/10.5604/01.3001.0010.7555Słowa kluczowe:

Class-D Digital Audio Amplifier, Digital Pulse Width Modulator (DPWM), Linearized Pulse Width Modulation (LPWM), Linearized Class-AD Double sided (LADD), Linearized Class-BD Double sided (LBDD), Programmable Tapped Delay Line (PTDL), Analog Delay Locked Loop (ADLL), Digital to Time Converter (DTC)Abstrakt

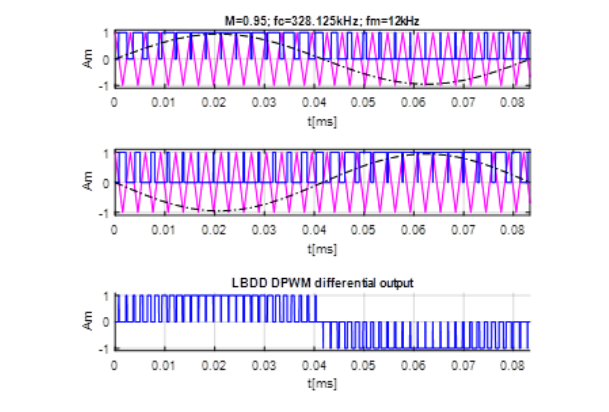

The paper presents an original architecture and implementation of 9-bit LBDD hybrid DPWM circuit for Class-BD digital audio amplifier. The input PCM signals are directly transformed into 24-bit LBDD DPWM signals and then are requanized to the 9-bit digital outputs using noise-shaping process to support high fidelity with practical values of time resolution, and finally are converted by the DTCs into the two physical trains of 1-bit PWM signals. The architecture of the proposed Class-BD hybrid DPWM circuit is composed of two Class-AD ones. The hybrid quantizer converts 6 MSB bits using counter method, based on the STM32F407xx microcontroller, while the remaining 3 LSB bits - using a method based on the Programmable Tapped Delay Line (PTDL). All necessary time waveforms are generated on the base of the internal microcontroller oscillator 168 MHz. The proposed 9-bit Class-DB DPWM circuit allows to attain SNR of 110 dB and THD about 0,2% within the audio baseband, at switching frequency of 328.1 kHz, clock frequency of 42 MHz and modulation index M = 0.95. Basic verification of algorithm and circuit operation as well as simulation and preliminary experimental results have been performed.

Statystyka pobrań

Bibliografia

M. Berkhout, L. Dooper, IEEE Transactions On Circuits And Systems-I: Regular Papers, 2010, 57, 991–1002. Google Scholar

R. Cellier, G. Pillonnet, A. Nagari, N. Abouchi, “An Review of Fully Digital Audio Class D Amplifiers Topologies”, Circuits and Systems and TAISA Conference, 2009. NEWCAS-TAISA ‘09. Joint IEEE North-East Workshop, June 28-July 1, 2009. Google Scholar

Ch. Morrison, S. Weiss, M. Macleod and R. Stewart, Comparison of Single- and Double-Sided Pulse Width Modulated Signalswith Non-Linear Predistortion, Proceedings of the 5th European DSP Education and Research Conference, 2012, Amsterdam. Google Scholar

S. M. Munk, K. S. Andersen, State of the Art Digital Pulse Modulated Amplifier System, AES 23rd Int. Conf, Copenhagen, Denmark, 2003 May 23–25. Google Scholar

C. Pascual, Z. Song, P. T. Krein, et. al., IEEE Transactions on Power Electronics, 2003, 18, 474–485. Google Scholar

M. Johansen, K. Nielsen, A Review and Comparison of Digital PWM Methods for Digital Pulse Modulation Systems, 107th AES Convention , 1999 September 24–27, New York. Google Scholar

F. Guanziroli, R. Bassoli, C. Crippa, D. Devecchi, and G. Nicollini., IEEE Journal Of Solid-State Circuits, 2012, 47, 686–698. Google Scholar

Luo Shumeng and Li Dongmei, Journal of Semiconductors, 2013, 34, 115001-1–115001-6. Google Scholar

L. Dooper, M. Berkhout, IEEE Journal Of Solid-State Circuits, 2012, 47, 1524–1534. Google Scholar

Jia-Ming Liu, Shih-Hsiung Chien, Tai-Haur Kuo, IEEE Journal Of Solid-State Circuits, 2012, 47, 1344–1354. Google Scholar

B. H. Gwee, J. S. Chang, H. Li, IEEE Transactions On Circuits And Systems -Ii: Analog and Digital Signal Processing, 2002, 49, 245–2256. Google Scholar

A. Syed, E. Ahmed, D. Maksimovic, E. Alarcon, Proc. IEEE Power Electron. Spec. Conf., 2004, 6, 4689–4695. Google Scholar

B. J. Patella, A. Prodic´, A. Zirger, D. Maksimovic´, IEEE Transactions on Power Electronics, 2003, 18, 438–446. Google Scholar

Xuzhen Shen, Xiaobo Wu, and Jing Lu, Lin Qin, Proceedings of the International MultiConference of Engineers and Computer Scientists, 2010, Vol II, IMCS 2010, March 2010. Google Scholar

J. Jasielski, S. Kuta, W. Machowski, W. Kołodziejski, Microelectronics Journal, 2014, 45, 1202–1211. Google Scholar

J. Jasielski, S. Kuta, W. Machowski, W. Kołodziejski, “Hybrid LBDD PWM Modulator for Digital Class-BD Audio Amplifier Based on STM32F407VGT6 Microcontroller and Analog DLL”, Mixed Design of Integrated Circuits & Systems (MIXDES), 2015 Proceedings of the 22st International Conference, 25–27 June 2015. Google Scholar

J. Jasielski, W. Kołodziejski, S. Kuta, W. Machowski, “An Analog Dual Delay Locked Loop Using Coarse and Fine Programmable Delay Elements”, Proceedings of the 20-th International Conference Mixed Design of Integrated Circuits & Systems (MIXDES), 2013, Gdynia, Poland, June, Pgs. 20–22. Google Scholar

RM0090 Reference manual. STM32F40xxx, STM32F41xxx, STM32F42xxx, STM32F43xxx advanced ARMbased 32-bit MCUs. Google Scholar

STM32F405xx STM32F407xx, Datasheet, June 2013, DocID022152 Rev 4. Google Scholar

UM1472 User manual Discovery kit for STM32F407/417 lines, January 2014 DocID022256 Rev 4. Google Scholar

Pobrania

Opublikowane

Jak cytować

Numer

Dział

Licencja

Prawa autorskie (c) 2017 Państwowa Wyższa Szkoła Zawodowa w Tarnowie & Autorzy

Utwór dostępny jest na licencji Creative Commons Uznanie autorstwa – Użycie niekomercyjne 4.0 Międzynarodowe.